USART简介

USART(Universal Synchronous/Asynchronous Receiver/Transmitter)通用同步/异步收发器

另外经常还会遇到串口叫UART,这里少了个s就是异步收发器,一般串口很少使用这个同步功能,所以 USART 和UART使用起来也没什么区别,其实这个STM32 的 USART 同步模式,只是多了个时钟输出而已,它只支持时钟输出,不支持时钟输入,所以这个同步模式更多的是为了兼容别的协议或者特殊用途而设计的,并不支持两个 USART 之间进行同步通信,所以我们学习串口主要还是异步通信。

USART是STM32内部集成的硬件外设,可根据数据寄存器的一个字节数据自动生成数据帧时序,从TX引脚发送出去,也可自动接收RX引脚的数据帧时序,拼接为一个字节数据,存放在数据寄存器里

串口主要就是靠收发约定好的波形来进行通信的,那这个 USART 外设就是串口通信的硬件支持电路, USART 大体可以分为发送和接收两部分,发送部分就是将数据寄存器的一个字节数据,自动转换为协议规定的波形,从TX引脚发送数据,接收部分就是自动接收RX引脚的波形,按照协议规定,解码为一个字节数据,存放在数据寄存器里,这就是 USART 电路的功能,当我们配置好了 USART 电路,直接读写数据寄存器就能自动发送和接收数据,使用还是非常方便的

自带波特率发生器,最高达4.5Mbits/s

波特率发生器,就是用来配置波特率的,它其实就是一个分频器,比如我们APB2总线给个72兆赫兹的频率,然后波特率发生器进行一个分频,得到我们想要的波特率时钟,最后在这个时钟下,进行收发,就是我们指定的通信波特率。

可配置数据位长度(8/9)、停止位长度(0.5/1/1.5/2)

这些就是STM32 USART 支持配置的参数了,这个数据位长度就是前面的参数,有八位和九位是包含奇偶 校验位 的长度,一般不需要 校验位 就选八位,需要 校验位 就选九位, 起始位 长度支持3种 起始位 (0.5/1/1.5/2),也就是在进行连续发送时, 起始位 长度决定了帧的间隔,最常用的就是1位 起始位 ,其他都很少用。

可选 校验位** (无校验/奇校验/偶校验)**

这里最常用的是无校验,那以上这些所有的参数,都是可以通过配置寄存器来完成的,使用库函数配置的话就更简单了,直接给结构体赋值就行,串口参数,最常用的就是波特率9600或者115200,数据位八位, 起始位 1位,无校验。,一般我们都选这种常用的参数,不用纠结的选它就是。

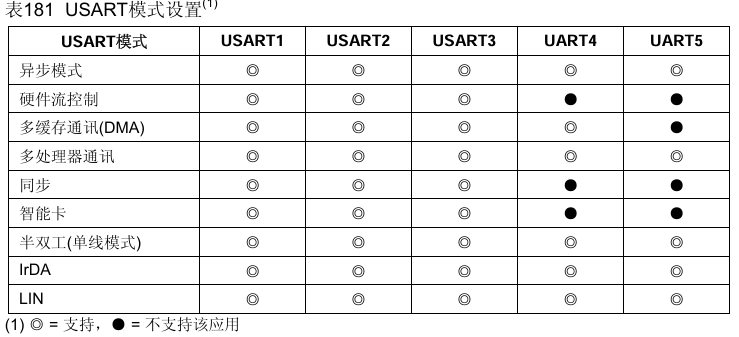

支持同步模式、 硬件流控制 、DMA、智能卡、IrDA、LIN

这个同步模式,就是多了个时钟clk的输出。

硬件流控制 ,这个是比如a设备有个TX向b设备的RX发送数据,a设备一直在发,发的太快了,b处理不过来,如果没有 硬件流控制 ,那b就只能抛弃新数据或者覆盖原数据了,如果有 硬件流控制 ,在硬件电路上会多出一根线,如果b没准备好接收就置高电平,如果准备好了就置低电平,a接收到了b反馈的准备信号,就只会在b准备好的时候才发数据,如果b没准备好,那数据就不会发送数据,这就是 硬件流控制 ,可以防止因为b处理慢而导致数据丢失的问题, 硬件流控制 STM32 也是有的,不过我们一般不用需要的。

串口支持DMA进行数据转运,如果有大量的数据进行收发,可以使用DMA转移数据,减轻cpu的负担。

最后智能卡、IrDA、LIN这些是其他的一些协议,因为这些协议和串口是非常的像,所以STM32 就对 USART 加了一些小改动,就能兼容这么多协议了,不过我们一般不用。

STM32F103C8T6 USART资源: USART1、 USART2、 USART3总共三个独立的 USART 外设

其中这里 USART1 是APB2 总线上的设备,剩下的都是APB1总线的设备,这个就开启时钟的时候注意一下,在使用的时候挂在哪个总线影响并不是很大。

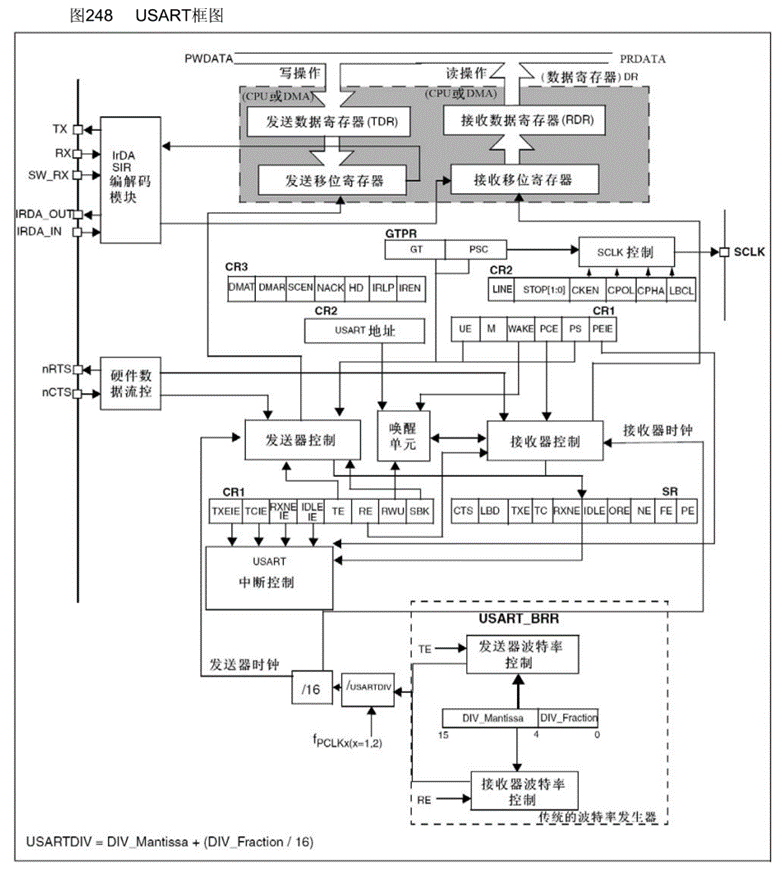

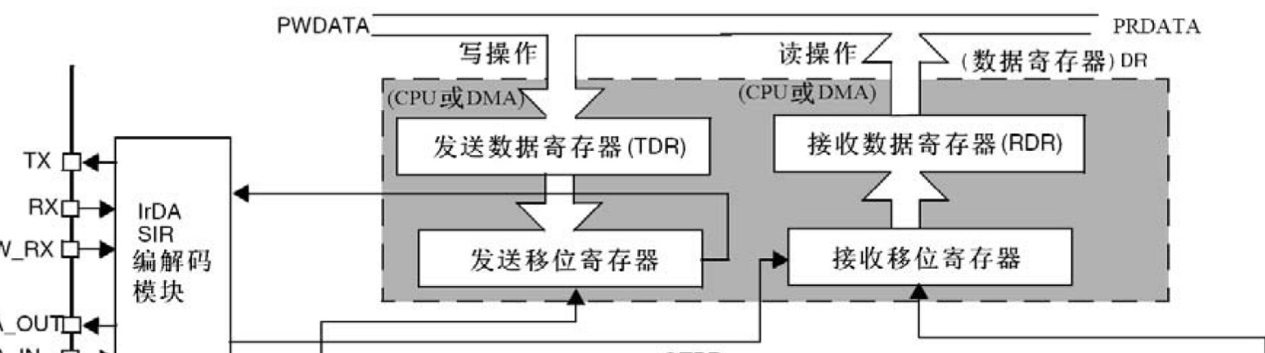

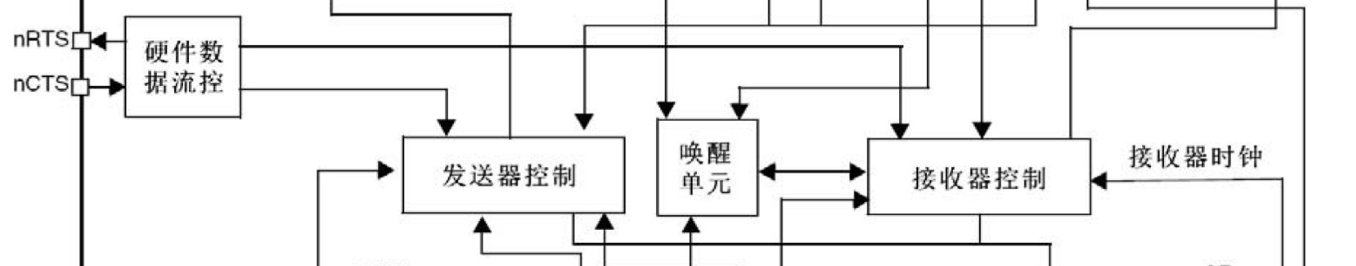

USART的框图

先看主体结构,先看左上这里的引脚部分,这里有TX和RX这两个就是发送和接收引脚,下下面这里的SW RX、IRDA OUT/IN这些是智能卡和IrDA通信的引脚,,引脚这块TX发送脚就是从发送移位寄存器接出去的,RX接收脚就是通向接收移位寄存器。

右边这一块,这部分就是串口的数据寄存器,发送或接收的字节数据就存在这里,上面只有两个数据寄存器 ,一个是发送数据寄存器 TDR(Transmit DR),另一个是 接收数据寄存器 RDR(Receive DR),这两个寄存器占用同一个地址,就跟51单片机串口的SBUF寄存器一样,在程序上只表现为一个寄存器,就是数据寄存器DR(Data Register),但实际硬件中是分成了两个寄存器,一个用于发送TDR,一个用于接收RDR,TDR是只写的,RDR是只读的,当你进行写操作时,数据就写到了TDR,当你进行读操作时,数据就是从RDR读出来的,然后往下看,下面是两个移位寄存器,一个用于发送,一个用于接收,发送移位寄存器的作用就是把一个字节的数据1位1位的移出去,正好对应串口协议的波形的数据位,这两个寄存器是怎么工作的呢,

举个例子,比如你在某时刻给TDR写入了0x55,这个数据在寄存器里就是二进制存储,0101 0101,那么此时硬件检测到你写入数据了,他就会检查当前移位寄存器是不是有数据正在移位,如果没有,这个0101 0101就会立刻全部移动的,发送移位寄存器准备发送,当数据从TDR移动到移位寄存器时,会置一个标志位,叫TXE(TX Empty),发送寄存器空,我们检查这个标志位,如果置1了,我们就可以在TDR写入下一个数据了,注意一下,当TXE标志位置1时,数据其实还没有发送数据,只要数据从TDR转移到发送移位寄存器来,TXE就会置1,我们就可以写入新的数据,然后发送移位寄存器就会在下面这里的发送器控制的驱动下向右移位,然后1位1位地把数据输出到TX引脚,这里是向右移位的,所以正好和串口协议规定的低位先行是一致的,当数据移位完成后,新的数据就会再次自动的从TDR转移到发送移位寄存器里来,如果当前移位寄存器移位还没有完成,TDR的数据就会进行等待,一旦移位完成,就会立刻转移过来。有了TDR和移位寄存器的双重缓存,可以保证连续发送数据的时候,数据帧之间不会有空闲,提高了工作效率,简单来说,就是数据一旦从TDR转移到移位寄存器了,不管移位有没有完成,就立刻把下一个数据放在TDR等着,一旦移完了,新的数据就会立刻跟上,这样做效率就会比较高。

接收端,这里也是类似的,数据从RX引脚通向接收移位寄存器,在接收器控制的驱动下,1位1位的读取RX电平,先放在最高位,然后往右移,移位八次之后,就能接收一个字节了,同样因为串口协议规定是低位先行,所以接收移位寄存器是从高位往低位这个方向移动的,之后当一个字节移位完成之后,这一个字节的数据就会整体的一下子转移到 接收数据寄存器 RDR,在转移的过程中也会置一个标志位,叫 RXNE (RX Not Empty),接收数据存器非空,当我们检测到 RXNE 置1之后,就可以把数据读走了,同样这里也是两个寄存器进行缓存,当数据从移位寄存器转移到RDR时,就可以直接移位接收下一帧数据了,这就是 USART 外设整个的工作流程。

到这里,这个外设的主要功能就差不多了,大体上就是数据运算器和移位寄存器,发送移位寄存器往TX引脚移位,接受移位寄存器从RX引脚移位,当然发送还需要加上帧头帧尾,接收还需要剔除帧头帧尾,这些操作它内部有电路会自动执行。

接着下面的控制部分和一些其他的增强功能,下面这里是发送器控制,它就是用来控制发送移位寄存器的工作的。接收器控制,用来控制接收移位寄存器的工作,左边这里有一个硬件数据流控,也就是 硬件流控制 ,简称流控,如果发送设备发的太快,接收设备来不及处理,就会出现丢弃或覆盖数据的现象,那有了流控就可以避免这个问题了,这里流控有两个引脚,一个是 nRTS ,一个是 nCTS , nRTS (Request To Send)是请求发送,是输出脚,也就是告诉别人,我当前能不能接受。 nCTS (Clear To Send)是清除发送,是输入脚,也就是用于接收别人 nRTS 的信号的,这里前面加个n意思是低电平有效。

那这两个硬件怎么工作的的呢?

首先得找另一个支持流控的串口他的TX接到我的RX,然后我的RTS要输出一个能不能接受的反馈信号,接到对方的CTS,当我能接受的时候,RTS就置低电平请求对方发送,对方的CTS接收到之后就可以一直发,当我处理不过来时,比如接收数据进器我一直没有读,又有新的数据过来了,现在就代表我没有及时处理,那RTS就会置高电平,对方CTS接收到之后就会暂停发送,直到这里 接收数据寄存器 被读走,RTS置低电平,新的数据才会继续发送。

反过来当我的TX给别人发送数据时,我们CTS就要接到对方的RTS用于判断对方能不能接受,TX和CTS是一对的,RX和RTS是一对的,CTS和RTS也要交叉连接,这就是流控的工作模式,当然我们一般不使用流控。

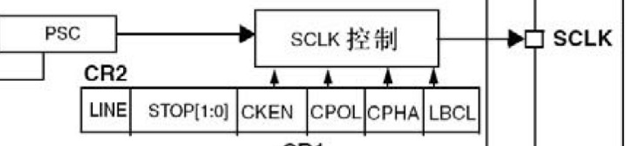

右边这个模块,这部分电路用于产生同步的时钟信号,它是配合发送移位寄存器输出的,发送寄存器每移位一次同步时钟电平就跳变一个周期,始终告诉对方,我移出去1位了,要不要让这个时钟信号来指导你接收一下,当然这个时钟只支持输出,不支持输入,所以两个usat之间不能实现同步的串口通信,

那这个时钟信号有什么用呢,第一个用途就是兼容别的协议,比如串口加上时钟之后,就跟SPI协议特别像,所以有了时钟输出的串口就可以兼容SPI,另外这个时钟也可以做自适应波特率,比如接收设备不确定发送设备给的是什么波特率,那就可以测量一下这个时钟的周期,然后再计算得到波折率,不过这就需要另外写程序来实现这个功能了,这个时钟功能一般不用,

中间这个唤醒单元,这部分的作用是实现串口挂载多设备,之前说过,串口一般是点对点的通信,点对点只支持两个设备互相通信,想发数据直接发就行,而多设备在一条总线上,可以接多个从设备,每个设备分配一个地址,想跟某个设备通信,就先进行寻址,确定通信对象,再进行数据收发,那回到这里,这个唤醒单元就可以用来实现多设备的功能,在这里可以给串口分配一个地址,当你发送指定地址时,此设备唤醒开始工作,当你发送别的设备地址时,别的设备就唤醒工作,这个设备没收到地址就会保持沉默,这样就可以实现多设备的串口通信了,这部分功能一般不用

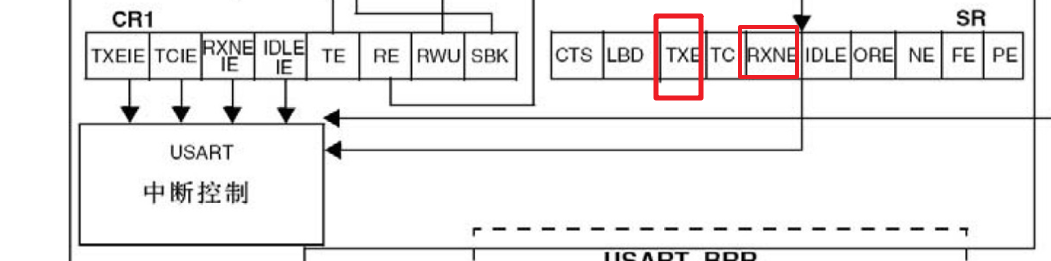

接着看下面这部分是中断输出控制,中断申请位,就是状态寄存器这里的各种标志位。状态寄存器有两个标志位比较重要,一个是TXE发送寄存器空,另一个是 RXNE 接收寄存器非空,这两个是判断发送状态和接收状态的必要标志位,,剩下的标志位了解一下就行。中断输出控制,这里就是配置中断是不是能通向NVIC。

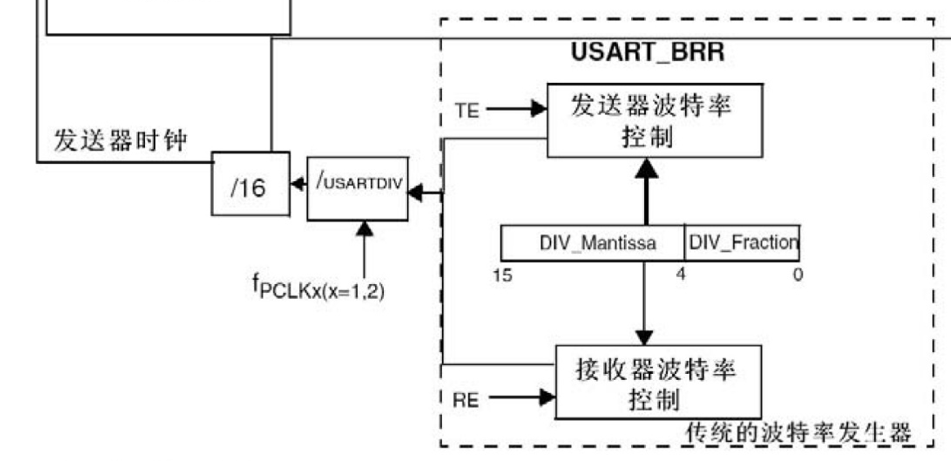

最下面这里是波特率发生器部分,,波特率发生器其实就是分频器,APB时钟进行分频,得到发送和接收移位的时钟,这里时钟输入是fPCLKx (x=1或2), USART1 挂载在APB2,所以就是PCLK2的时钟,一般是72M。其他的 USART 都挂载在APB1,所以是PCLK1的时钟,一般是36M,之后这个时钟进行一个分频,除一个 USART DIV的分频系数, USART DIV里面就是右边这样是一个数值,并且分为了整数部分和小数部分,因为有些波特率,用72兆除一个整数的话,可能除不尽会有误差,所以这里分频系数是支持小数点后四位的,分频就更加精准,之后分频完之后还要再除个16,得到发送器时钟和接收器时钟通向控制部分,然后右边这里,如果TE (TXEnable)为1,就是发送器使能了,发送部分的波特率就有效,如果RE(RX Enable)为1,就是接收器使能了,接收部分的波特率就有效

剩下还有一些寄存器的指示,可以自己看看手册里的寄存器描述。

串口的引脚定义

| STM32F103C8T6引脚定义表 | ||||||

|---|---|---|---|---|---|---|

| 引脚号 | 引脚名称 | 类型 | I/O口电平 | 主功能 | 默认复用功能 | 重定义功能 |

| 1 | VBAT | S | VBAT | |||

| 2 | PC13-TAMPER-RTC | I/O | PC13 | TAMPER-RTC | ||

| 3 | PC14-OSC32_IN | I/O | PC14 | OSC32_IN | ||

| 4 | PC15-OSC32_OUT | I/O | PC15 | OSC32_OUT | ||

| 5 | OSC_IN | I | OSC_IN | |||

| 6 | OSC_OUT | O | OSC_OUT | |||

| 7 | NRST | I/O | NRST | |||

| 8 | VSSA | S | VSSA | |||

| 9 | VDDA | S | VDDA | |||

| 10 | PA0-WKUP | I/O | PA0 | WKUP/USART2_CTS/ADC12_IN0/TIM2_CH1_ETR | ||

| 11 | PA1 | I/O | PA1 | USART2_RTS/ADC12_IN1/TIM2_CH2 | ||

| 12 | PA2 | I/O | PA2 | USART2_TX/ADC12_IN2/TIM2_CH3 | ||

| 13 | PA3 | I/O | PA3 | USART2_RX/ADC12_IN3/TIM2_CH4 | ||

| 14 | PA4 | I/O | PA4 | SPI1_NSS/USART2_CK/ADC12_IN4 | ||

| 15 | PA5 | I/O | PA5 | SPI1_SCK/ADC12_IN5 | ||

| 16 | PA6 | I/O | PA6 | SPI1_MISO/ADC12_IN6/TIM3_CH1 | TIM1_BKIN | |

| 17 | PA7 | I/O | PA7 | SPI1_MOSI/ADC12_IN7/TIM3_CH2 | TIM1_CH1N | |

| 18 | PB0 | I/O | PB0 | ADC12_IN8/TIM3_CH3 | TIM1_CH2N | |

| 19 | PB1 | I/O | PB1 | ADC12_IN9/TIM3_CH4 | TIM1_CH3N | |

| 20 | PB2 | I/O | FT | PB2/BOOT1 | ||

| 21 | PB10 | I/O | FT | PB10 | I2C2_SCL/USART3_TX | TIM2_CH3 |

| 22 | PB11 | I/O | FT | PB11 | I2C2_SDA/USART3_RX | TIM2_CH4 |

| 23 | VSS_1 | S | VSS_1 | |||

| 24 | VDD_1 | S | VDD_1 | |||

| 25 | PB12 | I/O | FT | PB12 | SPI2_NSS/I2C2_SMBAI/USART3_CK/TIM1_BKIN | |

| 26 | PB13 | I/O | FT | PB13 | SPI2_SCK/USART3_CTS/TIM1_CH1N | |

| 27 | PB14 | I/O | FT | PB14 | SPI2_MISO/USART3_RTS/TIM1_CH2N | |

| 28 | PB15 | I/O | FT | PB15 | SPI2_MOSI/TIM1_CH3N | |

| 29 | PA8 | I/O | FT | PA8 | USART1_CK/TIM1_CH1/MCO | |

| 30 | PA9 | I/O | FT | PA9 | USART1_TX/TIM1_CH2 | |

| 31 | PA10 | I/O | FT | PA10 | USART1_RX/TIM1_CH3 | |

| 32 | PA11 | I/O | FT | PA11 | USART1_CTS/USBDM/CAN_RX/TIM1_CH4 | |

| 33 | PA12 | I/O | FT | PA12 | USART1_RTS/USBDP/CAN_TX/TIM1_ETR | |

| 34 | PA13 | I/O | FT | JTMS/SWDIO | PA13 | |

| 35 | VSS_2 | S | VSS_2 | |||

| 36 | VDD_2 | S | VDD_2 | |||

| 37 | PA14 | I/O | FT | JTCK/SWCLK | PA14 | |

| 38 | PA15 | I/O | FT | JTDI | TIM2_CH1_ETR/PA15/SPI1_NSS | |

| 39 | PB3 | I/O | FT | JTDO | PB3/TRACESWO/TIM2_CH2/SPI1_SCK | |

| 40 | PB4 | I/O | FT | NJTRST | PB4/TIM3_CH1/SPI1_MISO | |

| 41 | PB5 | I/O | PB5 | I2C1_SMBAI | TIM3_CH2/SPI1_MOSI | |

| 42 | PB6 | I/O | FT | PB6 | I2C1_SCL/TIM4_CH1 | USART1_TX |

| 43 | PB7 | I/O | FT | PB7 | I2C1_SDA/TIM4_CH2 | USART1_RX |

| 44 | BOOT0 | I | BOOT0 | |||

| 45 | PB8 | I/O | FT | PB8 | TIM4_CH3 | I2C1_SCL/CAN_RX |

| 46 | PB9 | I/O | FT | PB9 | TIM4_CH4 | I2C1_SDA/CAN_TX |

| 47 | VSS_3 | S | VSS_3 | |||

| 48 | VDD_3 | S | VDD_3 |

复用功能这一栏就给出了每个 USART ,它的各个引脚都是复用在了哪个GPIO上的,比如这里 USART2 的TX是PA2口,RX是PA3口。 USART3 的TX和RX分别是PB10和PB11,然后 USART1 的TX和RX分别是PA9 和PA10,这些引脚都必须按照引脚定义里的规定来看。比如要使用 USART1 ,那TX必须是PA9,RX必须是PA10,或者看一下重映射,有没有重映射,这里有 USART1 的重映射,所以有机会换一次接口,剩下的引脚就没有机会做 USART1 的接口了,所以这个表在设计电路的时候很重要,要提前规划好引脚,别让引脚复用功能冲突了

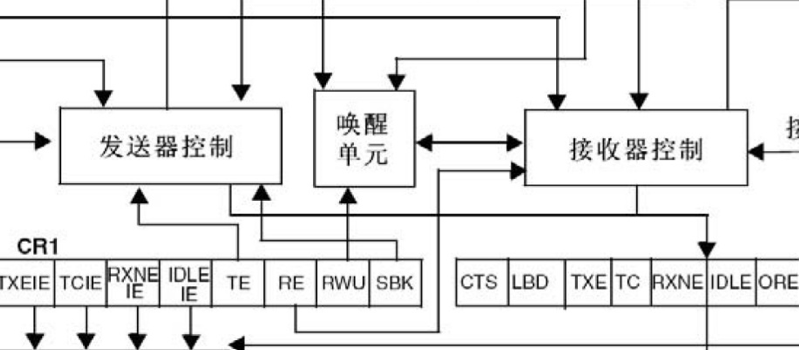

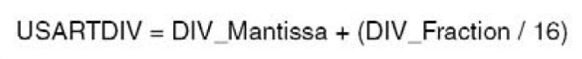

USART简化结构图

这就是 USART 最主要最基本的结构,最左边这里是波特率发生器,用于产生约定的通信速率,时钟来源是PCLK2/1经过波特预发器分频后产生的时钟,通向发送控制器和接收控制器,发送控制器和接收控制器用来控制发送移位和接收移位,之后由发送数据寄存器和发送移位寄存器,这两个寄存器的配合,将数据1位1位的移出去 ,通过GPIO口的复用输出,输出到TX引脚,产生串口协议规定的波形,这里画了几个右移的符号,就是代表这个移位寄存器是往右移的,是低位先行,当数据由数据运气转移到1位寄存器时,会制一个TXE的标志,为我们判断这个标志位就可以知道是不是可以写下一个数据了,然后接收部分也是类似的,RX引脚的波形通过GPIO口输入,在接收控制器的控制下,1位1位地移入接收移位寄存器,这里画了右移的符号,也是右移的,因为是低位先行,所以要从左边开始挤进来,移完一帧数据后,数据就会统一转运到 接收数据寄存器 ,在转移的同时,置一个 RXNE 标志位,检查这个标志位,就可以知道是不是收到数据了,同时,这个标志位也可以去申请中断,这样就可以在收到数据时直接进入中断函数,然后快速的读取和保存数据。

右边实际上有四个寄存器(发送数据寄存器**TDR、发送移位寄存器、接收移位寄存器、 接收数据寄存器** RDR),但是在软件层面只有一个DR寄存器可以供我们读写,写入DR时数据走上面这条路,进行发送。读取DR时,数据走下面这条路,进行接收,这就是 USART 进行串口数据收发的过程。

最后右下角一个开关控制,就是配置完成之后用Cmd开启一下外设,这个也是常规操作了。

数据帧

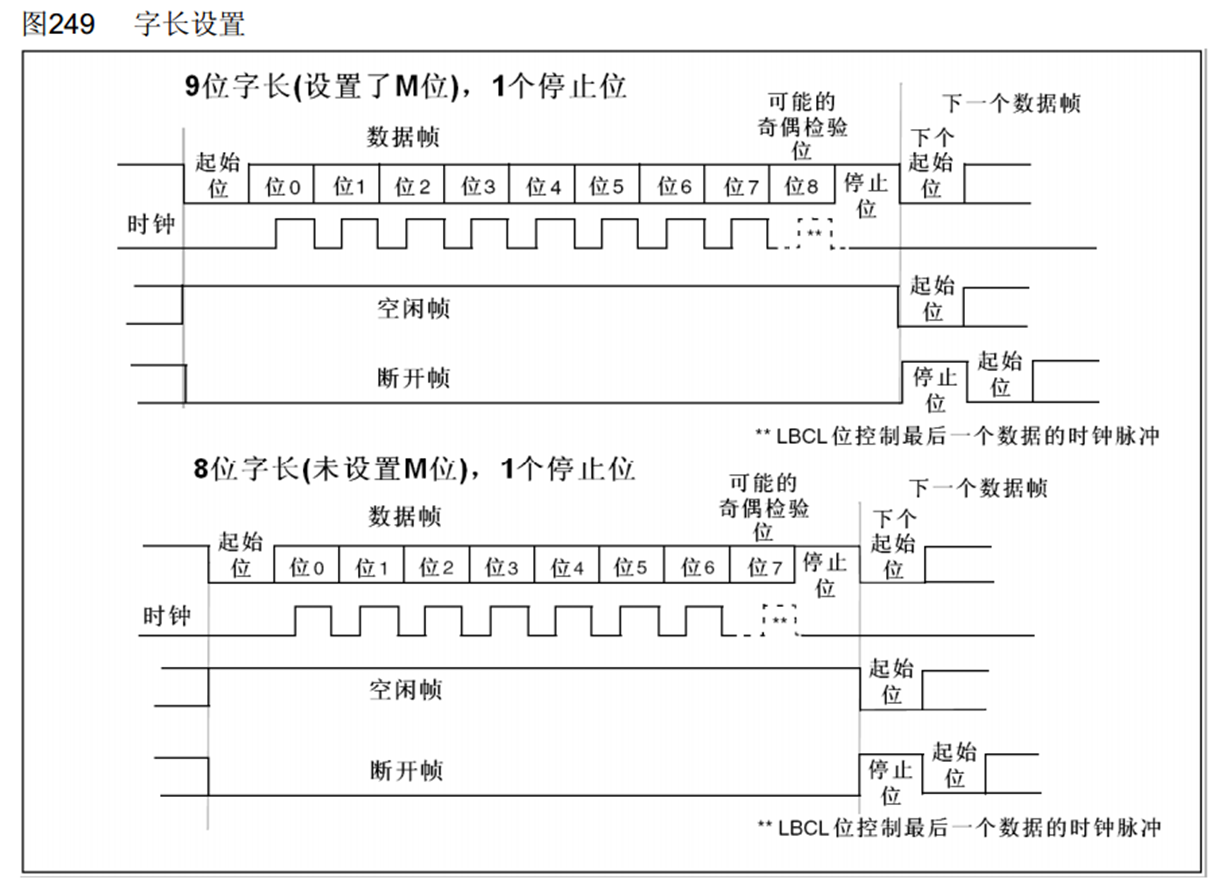

这个图是在程序中配置八位置长和九位置长的波形对比,这里的字长,就是前面说的数据位长度,它这里的日常是包含 校验位 的。

九位字长的波形

第一条时序很明显就是TX发送或者接收的数据帧格式空闲高电平,然后 起始位 0。然后根据写入的数据,置1或置0,依次发生位0到位8,加起来就是9位,最后 起始位 1,数据帧结束。在这里位8也就是第九个位置,是一个可能的奇偶 校验位 ,通过配置寄存器就可以配置成奇校验、偶校验或者无校验,这里可以选择配置成8位有效载荷+1位 校验位 ,也可以选择九位全都是有效载荷,不过既然你选择了九位字长,那一般都是要加上 校验位 的,因为八位有效载荷,正好对应一个字节。

下面这个时钟就是之前说的同步时钟输出的功能,可以看到,这里在每个数据位的中间都有一个时钟上升沿,时钟的频率和数据速率也是一样的,接收端可以在时钟上升沿进行采样,这样就可以精准定位每1位数据,这个时钟的最后1位,可以通过这个LBCL位控制,要不要输出,另外这个时钟的极性,相位什么的,也可以通过配置寄存器配置,需要的话可以了解一下

下面这两个波形,一个是空闲帧,就是从头到尾都是1。还有一个是断开帧,从头到尾都是0,这两个数据帧,是局域网协议用的,串口用不着不用管的

八位字长的波形

可以看到这里的数据位是从位0一直到位7,总共是八位,比上面这个少了一个位8,同样这个最后1位 位七,也是一个可能的奇偶 校验位 。还是同样,既然你选择了八位字长,那这里就最好选择无校验,要不然你 校验位 占1位,有效载荷就只剩七位了,一个字节都发不了,这不逼死强迫症吗

总的来说,这里有四种选择,九位字长有校验或无校验,八位字长有校验或无校验。但我们最好选择九位字长有校验,或八位字长无校验这两种。这样每帧的有效载荷都是一字节,这样才舒服,那最后这些时钟什么的和上面也都是类似的。

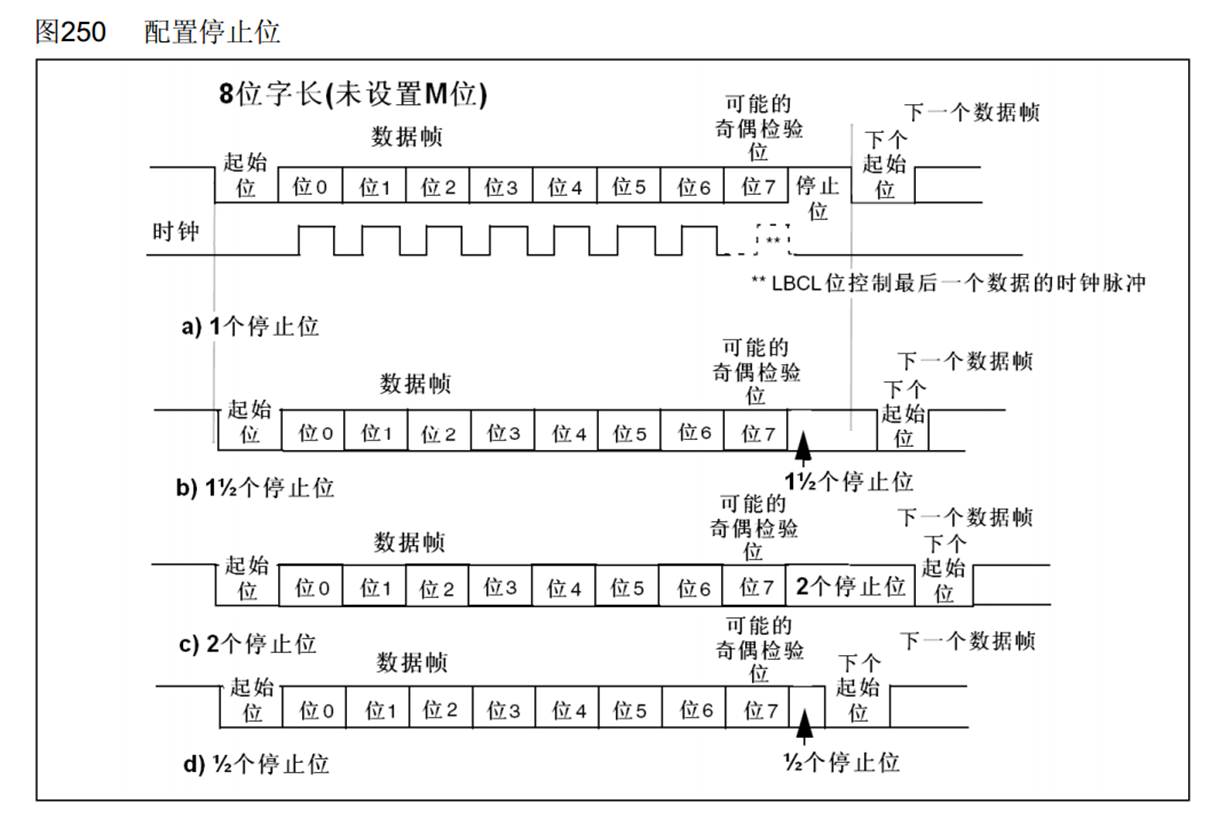

不同停止位的波形变化

STM32 的串口,可以配置 起始位 长度为0.5、1、1.5、2,这四种。这四种参数的区别,就是 起始位 的时长不一样。

第一个(a)是1个 起始位 ,这时 起始位 的时长就和数据位的1位时长一样。

第二个(b)是1.5个 起始位 ,这时的 起始位 就是数据位1位时长的1.5倍。

第三个(c)是2个 起始位 ,那 起始位 时长就是两倍。

第四个(d)是0.5个 起始位 ,时长就是0.5倍。

就是控制 起始位 时长的,一般选择1位 起始位 就行了,其他的参数不太常用

输入数据的一些策略

下面两个图展示的是 USART 电路输入数据的一些策略,对于串口来说,根据前面的介绍,可以想到串口的输出TX应该是比输入RX简单很多,输出就定时翻转TX引脚高低电平就行了。

但是输入就复杂一些,你不仅要保证输入的采样频率和波特率一致,还要保证每次输入采样的位置,要正好处于每1位的正中间,只有在每1位的正中间采样,这样高低电平读进来才是最可靠的,如果你采样点过于靠前或靠后,那有可能高低电平还正在翻转,电平还不稳定,或者稍有误差,数据就采用错了,另外输入最后还要对噪声有一定的判断能力,如果是噪声,最好能置个标志位提醒一下,这些就是输入数据所面临的问题。

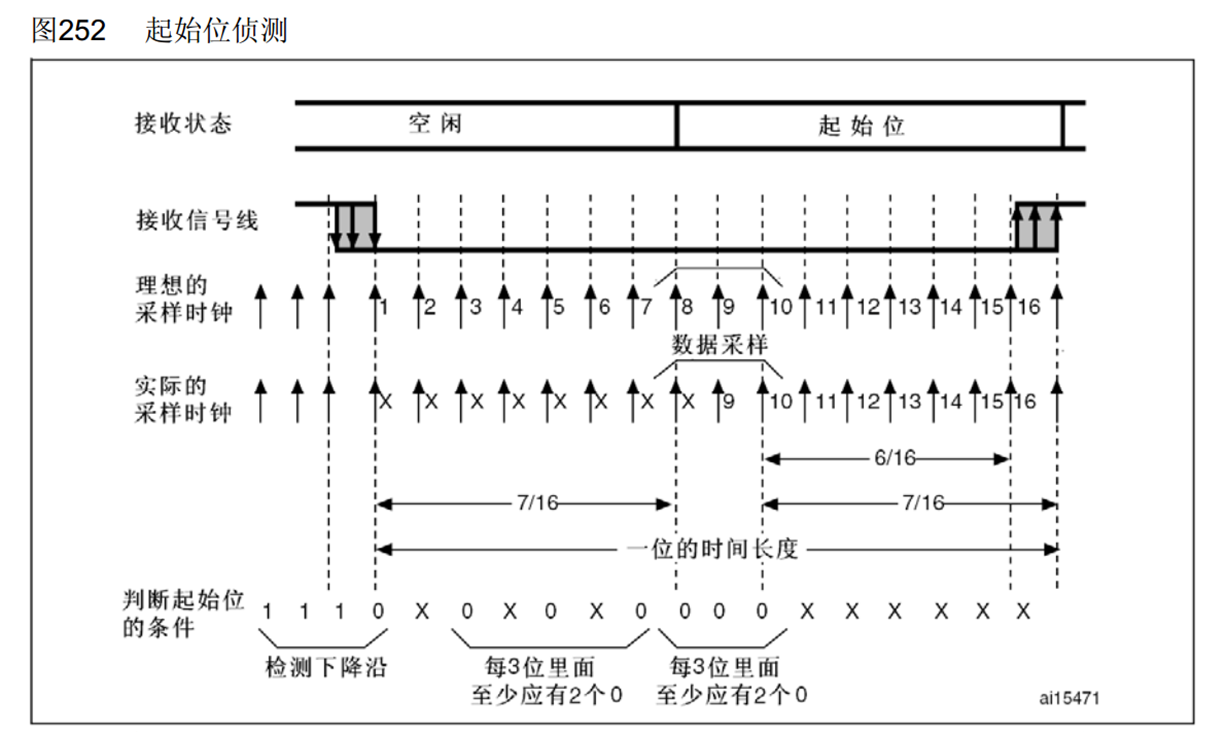

起始位 侦测

首先第一个图这里展示的是 USART 的 起始位 侦测,当输入电路侦测到一个数据帧的 起始位 后,就会以波特率的频率,连续采样一帧数据,同时从 起始位 开始,采样位置就要对齐到位的正中间,只要第1位对齐了,后面就肯定都是对齐的。

为了实现这些功能,首先输入的这部分电路对采样时钟进行了细分,它会以波特率的16倍频率进行采样,也就是在移位的时间里可以进行16次采样,然后它的策略是:最开始空闲状态高电平,那采样就一直是1,在某个位置突然采到一个零,那么就说明在这两次采样之间出现了下降沿,如果没有任何噪声,那之后就应该是 起始位 了,在 起始位 会进行连续16次采样,没有噪声的话,这16次采样肯定就都是0,这没问题,但是实际电路还是会存在一些噪声的,所以这里即使出现下降沿呢,后续也要再采样几次,以防万一。

根据手册的描述,还会在下降沿之后的第3次、5次、7次,进行一批采样,在第8次、9次、10次再进行一批采样,且这两批采样都要,要求每三位里面,至少应该有两个0。如果没有噪声,那肯定全是0,满足情况。如果有一些轻微的噪声,导致这里三位里面只有两个0,另一个是1,那也算是检测到了 起始位 。但是在状态进容器里会自一个NE(Noise Error)噪声标志位,就是提醒你一下数据我是收到了,但是有噪声,你悠着点用,如果这里三位里面只有一个0,那就不算监测到了 起始位 ,可能前面那个下降沿是噪声导致的,这时电路就忽略前面的数据,重新开始捕捉下降沿,这就是STM32 的串口在接收过程中对噪声的处理。如果通过了这个 起始位 侦测,那接收状态就由空闲变为接收 起始位 。同时,第8、9、10次采样的位置,就正好是 起始位 的正中间。之后,接收数据位时,就都在第8、9、10次,进行采样,这样就能保证采样位置在位的正中间了,这就是 起始位 侦测和采样位置对齐的策略。

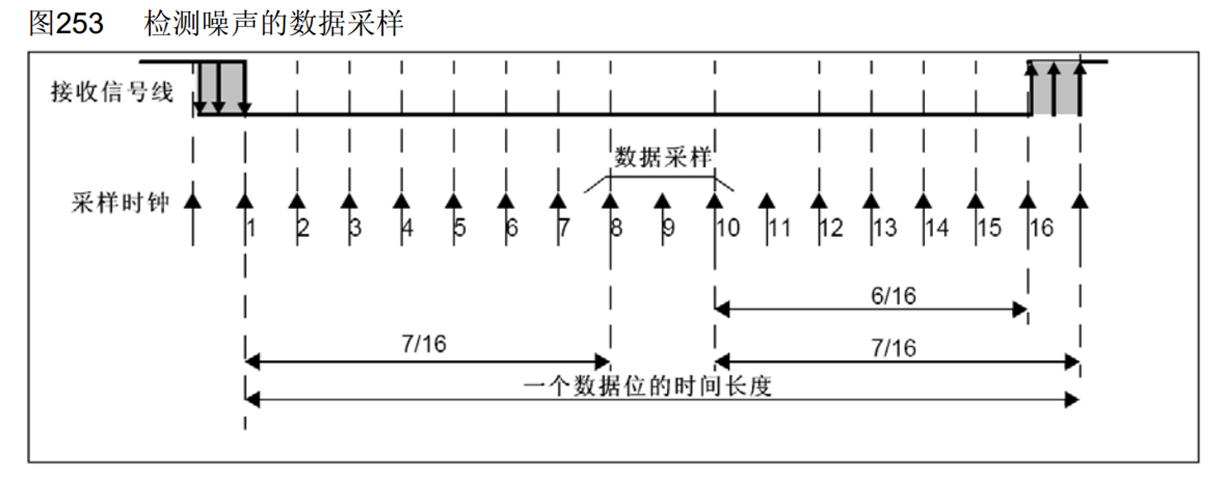

数据采样

那紧跟着我们就可以看这个数据采样的流程,这里从1到16是一个数据位的时间长度,在一个数据位有16个采样时钟,由于 起始位 侦测已经对齐了采样时钟,所以,这里就直接在第8、9、10次采样数据位。为了保证数据的可靠性,这里是连续采样三次。没有噪声的理想情况下,这三次肯定全为1或者全为0,全为1就认为收到了1,全为0就认为收到了0。如果有噪声导致三次采样不是全为1或者全为0,那它就按照二比一的规则来,两次为1就认为收到了1,两次为0就认为收到了0,在这种情况下,噪声标志位NE也会置1,告诉你我收到数据了,但是有噪声,这就是检测噪声的数据采样,可见STM32 对这个电路的设计考虑还是很充分的。

波特率发生器

波特率发生器就是分频器

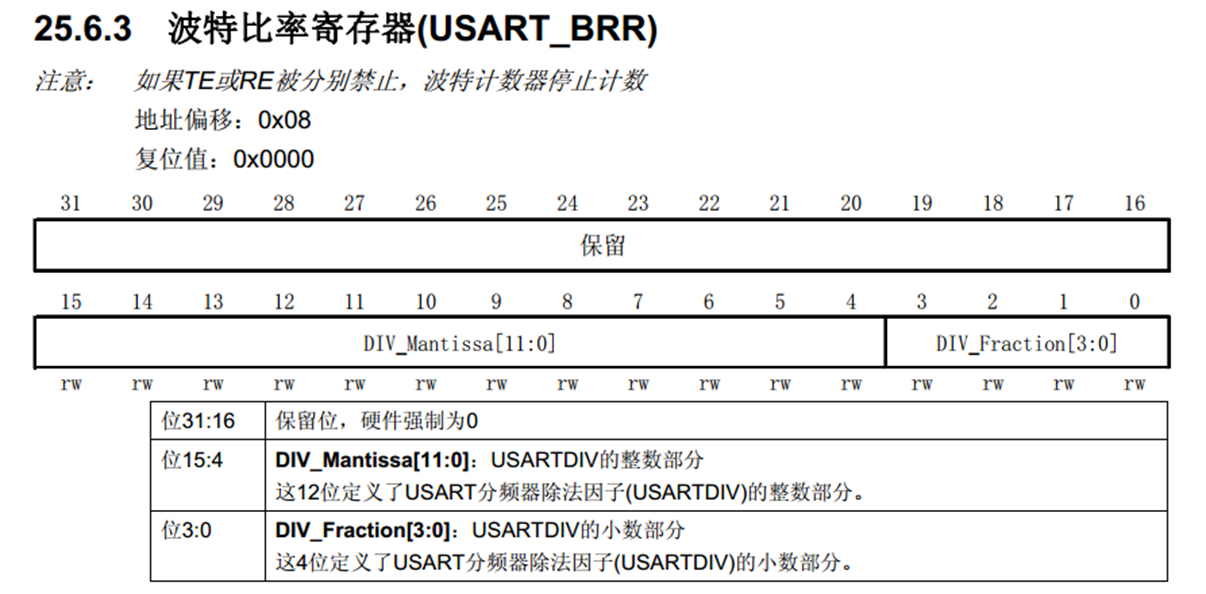

发送器和接收器的波特率由波特率寄存器BRR里的DIV确定,上面这个图就是BRR寄存器,里面就是分频系数DIV,DIV分为整数部分和小数部分,可以实现更细腻的分频。

波特率和分频系数的关系可以由这个计算公式进行计算

$$

波特率 =\frac{f_{PCLK2/1}}{(16 * DIV)}

$$

为什么这里多个16,因为它内部还有一个16倍波特率的采样时钟,所以这里输入时钟除以DIV要等于16倍的波特率,最终计算波特率自然要多除一个16了。

举个例子,比如我要配置 USART1 为9600的波特率,那如何配置这个BRR寄存器呢,我们代入公式

$$

9600 =\frac{72M}{(16 * DIV)}

$$

解得:

$$

DIV = \frac{72M}{\frac{9600}{16}}=468.75

$$

这是一个带小数的分频系数,最终写的寄存器还需要转换成二进制,最终得到二进制数是111010100.11,所以最终写的这个寄存器就是整数部分为11010100,前面多出来的补0(0000 1101 0100)。小数部分为11,后面多出来的补0(1100),这就是根据波特率写BRR寄存器的方法,不过用库函数配置的话就非常方便,需要多少波特率直接写就行了,库函数会自动帮我们算好。

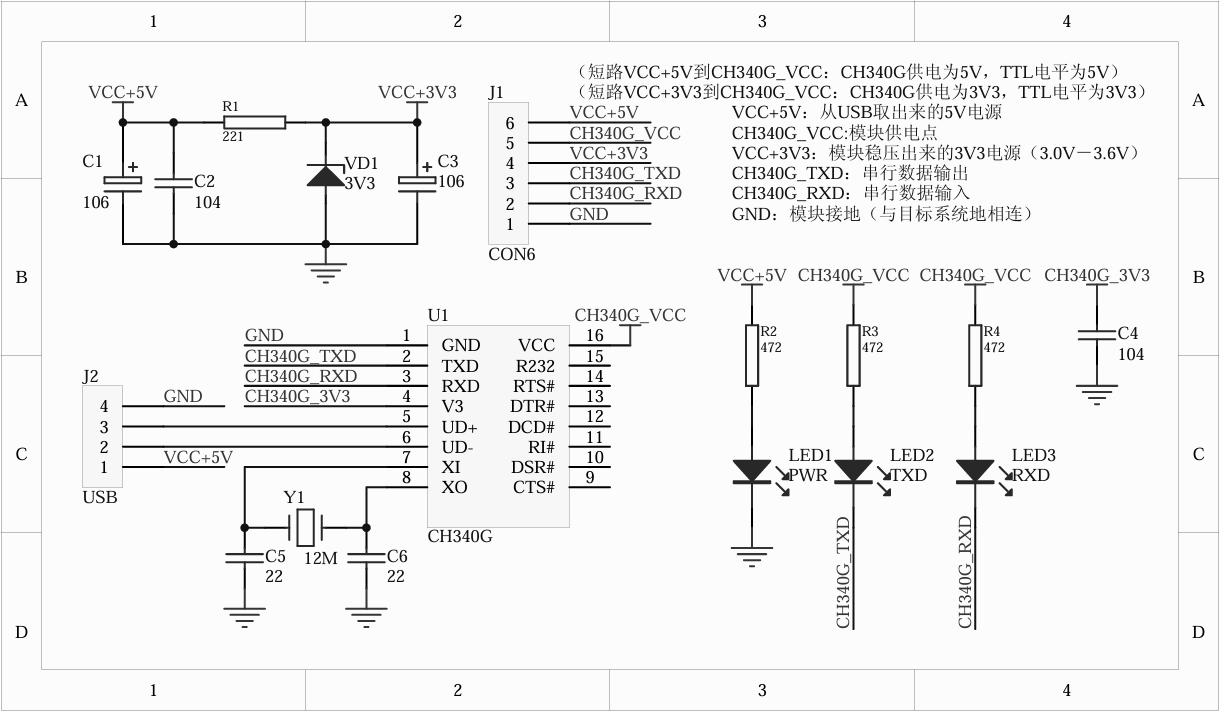

USB转串口模块的原理图

这个图展示的就是USB转串口模块的内部电路图,这里还有几点注意事项,大概看一下最左边这里J2是USB的端口,USB有4根线,GND、D+、D、VCC,USB标准供电是5伏,然后中间D+和D-是通信线,也是USB协议,所以这里需要加一个CH340 芯片转换一下,转换之后输出的就是TXD和RXD,是串口协议,最后通过J1排针引出来,那需要注意的就是这边的供电策略,首先所有的电都是从J1的VCC+5伏来的,然后VCC+5伏通过左上角稳压管电路进行稳压,得到VCC+3.3伏之后,VCC+5伏和VCC+3.3伏都通过排针引出来了,所以J1的第六脚和第四脚是分别由5伏和3.3伏输出的,那很多人迷惑的是这个第五脚,板子上标的是VCC这个引脚,通过原理图可以看到,它是通向了CH340 芯片的VCC上,所以这个第五脚实际上是CH340 的电源输入脚,一般模块的排针会有个跳线帽,这个跳线帽需要插在四五脚或者五六脚上,右边这里也有文字说明,短路5伏到VCC,CH340供电为5伏,TTL电平为5伏。短路3V3到VCC,CH340的供电为3.3伏,TTL电平为3.3伏。,所以这个跳线帽是用来选择通信电平的,也是给CH340芯片供电的,所以最好不要拿掉,如果你拿掉了,就相当于这整个芯片没有供电,那STM32通信需要3.3伏,所以把跳线帽插在这里的四五脚上就行了,那供电就只剩一个5V脚了,所以这个供电有点折磨人,要么选择5伏电平,剩下供电脚就只有3.3伏。要么选择3.3伏电平,剩下供电脚就是5伏,所以这个供电点的设计有点不太方便,不过考虑到电平的5伏和3.3伏可以互相兼容,所以如果你既需要通信又需要供电,那就保证供电是正确的就行了,通信电平没法一致,这应该也没问题

右边还有引脚说明,5伏脚是从USB取出来的,5伏电源输出。VCC是模块供电点。VCC+3V3: 模块稳压出来的3V3电源。TXD:串行数据输出。RXD:串行数据输入GND:模块接地(与目标系统地相连)

最后右下角这是指示灯和电源滤波,这里有PWR电源指示灯和TXD RXD的指示灯。

参考手册

第25章通用同步异步收发器

Hits: 122